Cell

Le Cell est un processeur conçu conjointement par IBM, Sony et Toshiba, révélé en février 2005. Il équipe surtout la console de jeu vidéo PlayStation 3 de Sony.

Recherche sur Google Images :

Source image : ensiwiki.ensimag.fr Cette image est un résultat de recherche de Google Image. Elle est peut-être réduite par rapport à l'originale et/ou protégée par des droits d'auteur. |

Page(s) en rapport avec ce sujet :

- Les processeurs Cell /B. E. offrent des performances inégalées qui accélèrent le traitement des tâches de calcul intensif, surtout celui des images et du ... (source : www-03.ibm)

- En revanche, certains types de calculs, entrant en compte dans le rendu... Le contrôleur mémoire est intégré au processeur Cell, comme pour les Athlon 64. (source : zeden)

- Pour rappel, le processeur Cell, particulièrement performant en calcul, a été conçu originellement pour des machines de jeux vidéo en 3D. [... ] Ce premier serveur'Cell', ... (source : recherche.silicon)

Le Cell est un processeur conçu conjointement par IBM, Sony et Toshiba, révélé en février 2005. Il équipe surtout la console de jeu vidéo PlayStation 3 de Sony. Il est envisagé de produire aussi des ordinateurs à base de Cell chez IBM, Mercury Computer Systems et Toshiba (Qosmio F50/55 et G50/55).

Ses champs de prédilection, appliqués aux calculs vectoriels à virgule flottante, sont :

- le jeu vidéo avec la console PlayStation 3 et les limites d'arcade (Namco Bandai) [1]

- les applications multimédia, films, TVHD (Sony, Toshiba)

- le rendu en temps réel, les simulations physiques, le traitement du signal (DSP)

- l'imagerie médicale, l'aérospatial et la défense, le calcul sismique, les télécommunications

Philosophie

Il est important de comprendre, au-delà des chiffres avancés par les concepteurs, la philosophie du Cell, radicalement différente des autres processeurs qui équipent, par exemple, les PC comme le Phenom d'AMD ou le Core 2 d'Intel.

Moins de complexité pour plus de puissance brute

En effet, les processeurs respectant les traditions ont développé ces dernières années, en amont des unités d'exécutions elles-mêmes, des unités d'optimisation du code informatique composant les programmes. Ceci favorise largement la tâche des programmeurs, et un code non optimisé peut fonctionner dans de bonnes conditions. À titre d'exemple, les processeurs respectant les traditions réorganisent le code en interne avant exécution, ils sont dits «OoO» (out of order). Les instructions peuvent être exécutées dans un ordre différent de celui donné par le programme. Après exécution, le processeur remet les instructions dans le bon ordre pour garantir le bon fonctionnement. Cela implique de plus un matériel de suivi (de traçabilité) des instructions au fur et à mesure de leur progression dans le pipeline. Tout ce travail consomme énormément de place (de transistors) sur le processeur.

Enfin, les processeurs respectant les traditions n'évoluent plus principalement depuis des années. Ils se contentaient principalement d'exploiter les nouveaux procédés de gravure pour monter en fréquence. Cette ère est terminée depuis le 90 nm, qui ne permet plus de monter en fréquence tout autant que par le passé. C'est pour cette raison qu'on assiste à l'émergence des processeurs double cœur : on exploite la nouvelle finesse de gravure pour mettre plus de transistors et développer le SMP à l'intérieur même du processeur, sans grande augmentation de fréquence.

IBM pour le Cell a choisi une approche originale. Le Cell, tout comme les processeurs du passé, ne fait aucun travail de réorganisation du code, il est dit «in order». Cela libère énormément de place pour ajouter de nouvelles unités d'exécution. L'inconvénient est que le travail d'optimisation est à la charge du programmeur et du compilateur et nuit par conséquent à l'interopérabilité. Le déplacement d'un travail hors du processeur avait déjà prévalu pour le RISC.

Une autre originalité du Cell, c'est qu'il est optimisé pour le calcul distribué : plusieurs processeurs peuvent communiquer entre eux et partager leur charge de travail. Ainsi, plus on possède de processeurs Cells, plus on a une puissance de calcul importante à disposition.

Les performances maximales théorique (peak) du processeur Cell @3, 2 GHz avec 8 SPEs, atteintes lors de calculs vectoriels, sont :

- en simple précision 32 bits (SP) : 230, 4 GFLOPS (25, 6 GFLOPS par SPE, 25.6 GFLOPS pour le PPE)

- en double précision 64 bits (DP) : 20, 8 GFLOPS (1.8 GFLOPS par SPE, 6.4 GFLOPS pour le PPE)

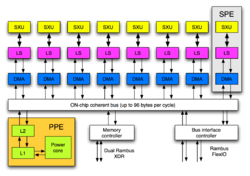

Un cœur principal et huit cœurs spécifiques

Plutôt que de dupliquer plusieurs fois le même cœur semblable, comme sur les processeurs multi cœur classiques, les concepteurs ont choisi une toute autre approche : 1 cœur principal, et 8 cœurs spécifiques.

Le cœur principal, dit PowerPC Processing Element ou PPE, reste assez proche d'un cœur classique : même si comme nous l'avons vu sa conception est simplifiée, surtout avec l'absence de module d'optimisation, le jeu d'instruction IBM POWER, bien connu, permet un accès à la RAM via un dispositif de cache à deux niveaux L1 et L2. Ainsi, le PPE est la partie du Cell la moins exotique.

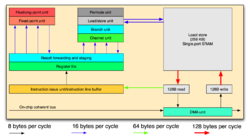

Chacun des 8 cœurs spécifiques, dit Synergystic Processing Elements ou SPE, est constitué de 2 parties : une mémoire locale (Local Storage ou LS) de 256 Ko et une unité de calcul vectoriel dite Streaming Processor Unit ou SPU. Pourvus d'un jeu d'instruction SIMD spécifique mais se rapprochant de AltiVec, les SPU ont un accès direct et extrêmement rapide à leur mémoire locale. Par contre, pour accéder à la mémoire principale ils doivent effectuer une requête de transfert asynchrone à un bus d'interconnexion.

Ce bus d'interconnexion dit Element Interconnect Bus ou Bus EIB est le dernier élément particulièrement important du Cell. Son rôle est d'établir la connexion entre le PPE, les SPE, la mémoire RAM principale, et les périphériques d'entrée-sortie.

Pour résumer et simplifier :

- le PPE se charge de préparer le travail et de démarrer les SPE (c'est légèrement un rôle de chef d'orchestre). Il sert aussi à effectuer l'ensemble des tâches qui ne peuvent pas simplement être effectuées sur les SPE.

- Les SPE exécutent ainsi les calculs les plus complexes à la demande du PPE en récupérant les données dans leur mémoire locale grâce à l'EIB.

- Enfin, pour maximiser les performances en évitant d'attendre l'EIB, le code s'exécutant sur un SPU doit effectuer ses calculs en même temps qu'ont lieu les transferts, par exemple en utilisant plusieurs mémoires tampons.

Architecture

Il dispose de 234 millions de transistors gravés sur une surface de 235 mm2 en 90 nm SOI (Silicon On Insulator). La version finale tourne à 3, 2 GHz en 0, 9 V et est constituée de huit couches de cuivre interconnectées. Le contrôle de la température est dynamique : dix capteurs thermiques numériques et un capteur linéaire.

Un processeur CBE (Cell Broadband Engine) se compose de :

- 1 PPE (PowerPC Processing Element) : unité généraliste simplifiée, «in order»

- 8 SPEs (Synergistic Processing Element) ou «SIMD processing unit» pour certains auteurs

- Un cache de niveau 2 de 512 Ko partagé

- l'EIB (Element Interconnect Bus) qui gère les communications internes entre les différents éléments

- MIC (Memory Interface Controler) : contrôleur mémoire partagé

- Flex I/O interface : contrôleur d'entrées/sorties (E/S)

Le mot cell veut dire cellule en anglais. Le processeur se décompose en effet en plusieurs cellules. Une cellule est un ensemble constitué par le PPE et un SPE. Cette unité matérielle indépendante peut être affectée à un thread. La répartition des tâches selon les cellules est l'enjeu pour le programmeur qui souhaite utiliser au mieux ce processeur.

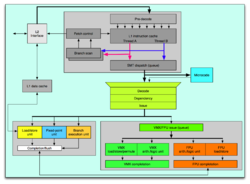

Le PowerPC Processing Element

Le cœur (PPE) utilise les jeux d'instructions IBM POWER et AltiVec, les nombres entiers, et la répartition du travail entre les SPEs. C'est un processeur 64 bits, «In Order», et SMT deux voies. Il a une mémoire cache intégrée de niveau 1 de 32 Ko.

Les Synergistic Processing Element

Ils se destinent au calculs SIMD. Un SPE correspond à un processeur vectoriel indépendant possédant 128 registres 128 bit, 4 unités de calcul en virgule flottante double précision et 4 unités de calcul entiers. Il effectue deux instructions par cycle d'horloge. Il inclut une mémoire locale de 256 Ko de type SRAM haute vitesse. Un processeur Cell contient 8 SPEs.

Celui de la PS3 n'aura que 7 unités fonctionnelles. Les différentes hypothèses à ce sujet sont :

- limiter le nombre de rejet en sortie d'usine ;

- gérer les DRMs et de la sécurité[2] ;

- garantir le fonctionnement de la PS3 en cas de défaillance matérielle d'un cœur durant la durée de vie de la console.

L'Element Interconnect Bus

Comporte 4 boucles 128 bit supportant des transferts multiples. Il relie l'ensemble des composants du CELL entre eux : PPE, SPEs, cache L2 et contrôleurs mémoire et entrées/sorties.

Contrôleurs mémoire et entrée/sortie

Le MIC est un double contrôleur mémoire XDR (XDRAM) offrant un débit de 25, 6 Go par seconde. On trouve deux interfaces E/S configurables (76, 8 Go/s, 6, 4 Gbit/s) (Flexible I/O)

Système

Annoncé le 29 juin 2005, le noyau du dispositif d'exploitation Linux supportera ce processeur CELL : Annonce du port de Linux sur le processeur CELL - 29 juin 2005

On peut voir dans le ChangeLog, les changements intervenus pour la version 2.6.16 avec la précédente - 20 mars 2006 permettant à Linux de tourner à partir de cette version du noyau.

À partir de la version 2.6.16 du noyau Linux, vous pouvez consulter et utiliser la documentation du dispositif de fichier virtuel de contrôle des SPUs en anglais.

Depuis le 14 juillet 2006, est accessible en anglais, en version SDK 1.1 et pour partie sous distribution Fedora core 5, la totalité des logiciels et documentation indispensable au développement ainsi qu'à la compilation pour le processeur CELL sous Linux, cf. Informations about how to enable linux on Cell Broadband Engine™ based systems par (en) Barcelona Supercomputing Center (BSC) .

L'accélération 3D libre pour le processeur CELL est ajouté en janvier 2008 avec une première version rudimentaire d'un pilote pour Gallium 3D le futur remplaçant de Mesa 3D, implémentation libre d'OpenGL[3]..

Calcul à Haute Performance

| Machine / processeur (s) | #proc | #core

par proc |

Rmax (GFlop/s) | Rpeak (GFlop/s) | Rmax (GFlop/s)

par proc |

Rpeak (GFlop/s)

par proc |

|---|---|---|---|---|---|---|

| IBM Cell BE (3, 2 GHz) ¹¹¹ en 2006 | 1 | 9 | 98.05 | 14.6 (64 bit)

204.8 (32 bit) |

98.05 | 14.6 (64 bit)

204.8 (32 bit) |

| Itanium 2 Montecito (2× Itanium 2 @ 1, 6 GHz) | 1 | 2 | (∼12) ¹ | 12.8 | (∼12) ¹ | 12.8 |

| IBM Cell BE (3, 2 GHz) en 2005 | 1 | 9 | (10∼13) ¹ | 14.6 | (10∼13) ¹ | 14.6 |

| Pentium 4 + SSE3 (3, 6 GHz) | 1 | 1 | 14.4 | 14.4 | ||

| IBM IntelliStation POWER 285 (2× POWER5+ @ 1, 9 GHz) | 2 | 1 | 14.35 | 15.2 | 7.18 | 7.6 |

| HP Integrity rx1620-2 (2× Itanium 2 @ 1, 6 GHz) | 2 | 1 | 12.05 | 12.8 | 6.03 | 6.4 |

| Pentium 4 (3, 2 GHz) | 1 | 1 | 6.4 | 6.4 | ||

| HP ProLiant BL25p (2× AMD 254 Opteron @ 2, 8 GHz) | 2 | 1 | 11.2 | 5.6 |

Sources : LINPACK benchmark sur de nombreuses machines du 20 juillet 2006 au format ps - et - IBM performance - Tableau 9 du 29 novembre 2005

¹ valeurs estimées

¹¹¹ L'algorithme utilisé pour obtenir cette performance est basé sur une approche de raffinement itérative où un couple de 32 et 64 bits en virgule flottante sont utilisés. Cette méthode calcule une factorisation LU en 32 bits et utilise une approche de raffinement itérative où est choisie la solution avec une précision de 64 bits. La précision obtenue est équivalente à une implémentation 64 bits. Dans notre cas, le Rpeak est noté par un couple de 32 et 64 bits en virgule flottante.

- L'aspect négatif de cette approche est que celle-ci nécessite une fois et demi plus de mémoire qu'une approche normale de factorisation LU en 64 bits. Pour plus d'information voir : Exploitation du calcul en simple précision pour une exacte résolution en double précision.

- L'aspect positif de cette approche est que celle-ci permet d'utiliser les énormes capacités de calcul du processeur CELL en 32 bits soit 204, 8 GFLOP/s, au lieu de plafonner en 64 bits à 14, 6 GFLOP/s (mais néanmoins supérieures aux autres processeurs actuels - 2006).

À noter que, certains des processeurs utilisés pour les Calculs Haute Performance démontrent actuellement la supériorité des performances lors de calculs 32 bits comparé à des calculs directement réalisés en 64 bits, comme les processeurs AMD Opteron, Intel Pentium, IBM PowerPC, et Cray X1.

Applications

Sony

Application la plus connue, la console de jeux vidéo PlayStation 3 de Sony est conçue autour du processeur CELL.

Pour des raisons de coûts de production, un des huit SPEs est inutilisé afin d'obtenir un rendement de production plus élevé (Sony peut utiliser les processeurs avec 1 ou 0 SPE défectueux). Le processeur CELL de la PS3 aura ainsi 7 SPE au contraire de la version standard d'IBM à 8 SPE[2].

Mercury

Mercury et IBM ont collaboré pour développer des solutions basées sur le processeur CELL.

Mercury propose au 1er juillet 2006 quatre solutions à base de processeurs CELL, plus une solution d'évaluation (performance peak simple précision) :

- 200 GFLOPS «PowerBlock™ 200» Châssis ATR pour véhicule militaire terrestre contenant 1 processeur CELL @3 GHz, soit la capacité de 45 processeurs Intel Pentium 4 Xeon® @2, 2 GHz

- 410 GFLOPS «1U Dual Cell-Based Server» Un serveur rack composé de 2 processeurs CELL @3, 2 GHz

- 16 TFLOPS «Dual Cell-Based Blade» Une lame à 2 processeurs CELL offrant une performance maximale de 400 GFLOPS, pouvant être monté avec 6 châssis de BladeCenter contenant chacun 7 lames.

- 25 TFLOPS «Turismo Cell-Based System» Un package à 4 processeurs CELL offrant une performance maximale de 800 GFLOPS, pouvant être monté avec 6 châssis de 5 package à 4 processeurs chacun pour une taille totale réduite.

- Un dispositif d'évaluation de la technologie CELL «Cell Technology Evaluation System (CTES) » Un châssis BladeCenter de 7 lames contenant chacun 2 processeurs CELL @2, 4 GHz.

IBM

IBM annonce une nouvelle génération de serveurs lame et la formation officielle de la communauté Blade qui regroupent des acteurs participent au développement de solutions BladeCenter.

Ce serveur lame (utilisé pour le nouveau BladeCenter H) regroupe 9 processeurs CELL, constituant la première offre de ce type chez IBM. Conçu pour les traitements de calcul intensif et les applications multimédia à forte demande en bande passante, il permet d'augmenter de manière significative la bande-passante des petits serveurs lames, et offre ainsi aux entreprises la possibilité de faire circuler 10 fois plus de données sur leur réseau. Cette percée technologique repousse les limites des performances internes des nouveaux dispositifs en leur fournissant plus de 40 Gbits/s (Gb) de bande-passante I/O par lame.

Annoncé en septembre 2006, Roadrunner est le premier supercalculateur à utiliser ce processeur (16 000 processeurs de ce type). Il est construit par IBM.

Les enjeux scientifiques et industriels du CELL

Si le processeur CELL a été, originellement conçu pour les consoles de jeux, sa particulièrement grande puissance de calcul le rend particulièrement attractif dans de nombreux domaines comme le calcul intensif (HPC), le traitement d'images (TI) et la vision industrielle (VI). Sa complexité rend le portage d'applications particulièrement complexe car il faut optimiser les calculs et les transferts. Optimiser les transferts veut dire optimiser deux types de transferts : ceux depuis la mémoire externe vers un SPE et ceux entre SPE. Cela revient à implémenter des modèles de transfert pour des calculs dits SIMD ou pipeline. Optimiser un code SPE, n'est alors pas plus compliqué que d'optimiser un code sur un processeur Altivec. Le jeu d'instruction est particulièrement proche et supporte les calculs en flottant et en entiers. Fin 2007, seules deux équipes de R&D au monde ont réussi cela, la société Rapidmind racquise en aout 2009 par Intel[4] et l'équipe AXIS de l'IEF (Institut d'Electronique Principale) (Université Paris Sud). Rapidmind a l'avantage de pouvoir en plus déployer du code sur GPU (carte 3D NVidia et AMD-ATI).

Une nouvelle version du Cell

Sony a livré plus d'informations sur la nouvelle révision 65 nm du processeur Cell Broadband Engine, aujourd'hui en production massive pour remplacer la première version du processeur gravée en 90 nm.

Le Cell en 65 nm viendra surtout remplacer son prédécesseur dans les PlayStation 3 de Sony, il aura l'avantage d'être 40 % plus petit que la version 90 nm, et en particulier de moins chauffer. L'actuelle version 90 nm du processeur a un die tellement grand (222 mm²) que cela pose un réel problème de rendement, car Sony peut alors en placer moins sur une même galette de silicium (wafer). Avec une réduction de la surface du die du processeur de 40 %, la production pourra atteindre des rendements énormément plus profitables.

Cette amélioration de rendement sera au moins aussi importante lors du passage du 65 nm au 45 nm, que Sony prévoit pour la première moitié de l'année 2009. Tous ces processeurs sont gravés grâce à la technologie SOI (Silicon On Insulator), utilisée par IBM et AMD.

En chauffant moins, le Cell en 65 nm va aussi pouvoir atteindre des fréquences plus élevées. Sony annonce jusqu'à 6 GHz sous une tension d'1, 3 V, à l'endroit où le Cell 90 nm ne pouvait atteindre que 5, 2 GHz, à la limite de ses capacités. Sur une tension d'1 V, le Cell 65 nm atteint les 4 GHz sans problème.

Cette montée en fréquence est aussi due à la séparation de l'alimentation de la SRAM (mémoire cache du processeur) et du reste de la puce. Deux lignes de tension indépendantes pour perfectionner les performances et la consommation du processeur.

Notez que IBM compte bien utiliser sa dernière trouvaille, l'eDRAM, dans une prochaine génération de processeurs Cell.

Voir aussi

Liens externes

Dossiers de présentation du CELL :

- (fr) Le processeur Cell sur presence-pc. com

- (en) Article détaillé sur le CELL sur RWT

- (en) Le CELL sur Ars Technica partie I

- (en) Le CELL sur Ars Technica partie II

- (en) Taux de rejet industriel de la puce Cell (Les puces, avec des cores dégradés parmi les 8 spécifiques, restent utilisables avec ceux toujours fonctionnels)

Articles d'étude approfondie du CELL :

- (en) Potentiel du processeur CELL pour les calculs scientifiques par S. Williams & collaborateurs de la division recherche computationnelle du laboratoire de Berkeley

- (en) Explication de l'architecture CELL par Nicholas Blachford en 2005 selon les publications de Sony, Toshiba, IBM et Rambus

- (en) Exploitation du calcul en simple précision pour une exacte résolution en double précision

- (en) Moins est mieux : Exploitation du calcul mathématique en simple précision pour les dispositifs de Calcul à Haute Performance (HPC)

Documentations techniques constructeurs CELL :

- (en) L'architecture CELL sur IBM Research

- (en) Documentation, développement et spécification de la puce CELL par IBM

- (en) Documentation, développement et spécification du CELL par Sony

- (en) IBM - exemples d'applications / performances / caractéristiques

Documentations techniques de développement logiciels pour CELL :

- (en) Informations about how to enable linux on Cell Broadband Engine™ based systems par (en) Barcelona Supercomputing Center (BSC)

- (en) CELL BE SDK 2.0

- [pdf] (en) Cell BE Programming Handbook par IBM, de 9, 56 Mo.

- (en) Cell programming présenté à Georgia Tech par IBM.

Parallélisation automatique sur le Cell

Notes et références

- ↑ Namco Bandai : l'arcade avec le Cell, 27 mars 2007, PlayFrance

- (en) Revolution disclosures, and a PS3 tidbit sur Ars Technica

- ↑ (en) added Cell driver page dans le changelog GIT de Mesa 3D

- ↑ "RapidMind + Intel"], Intel Blog (19-08-2009)

Recherche sur Amazone (livres) : |

Voir la liste des contributeurs.

La version présentée ici à été extraite depuis cette source le 07/04/2010.

Ce texte est disponible sous les termes de la licence de documentation libre GNU (GFDL).

La liste des définitions proposées en tête de page est une sélection parmi les résultats obtenus à l'aide de la commande "define:" de Google.

Cette page fait partie du projet Wikibis.

Accueil

Accueil Recherche

Recherche Début page

Début page Contact

Contact Imprimer

Imprimer Accessibilité

Accessibilité